随着人工智能产业需求的快速发展,供应链对创新的需求比以往任何时候都更加迫切,这也是台积电等公司追求将新技术融入现有产品的原因。Ctee现在报道称,这家台湾巨头计划开发一种新的 “CoW-SoW “高级封装技术,据说这种技术可以将内存和逻辑芯片堆叠在一个接口上,从而提供更快的性能,并提高板载芯片间桥接的精度。

CoWoS-L封装技术使用LSI(本地硅互连)桥接RDL(硅中介层)连接晶粒,传输速度可达10/TBs左右;不过封装步骤由于桥接放置精度要求极高,稍有缺陷都可能导致价值4万美元的芯片报废,从而影响良率及获利。

相关人士透露,由于GPU晶粒、LSI桥接、RDL中介层和主基板之间的热膨胀系数(CTE)相异,导致芯片翘曲、系统故障。为提升良率,辉达重新设计GPU芯片顶部金属层和凸点。不只是AI芯片RTO(重新流片)修改设计,据供应链透露,准备发布之50系列的显卡也需要RTO,上市时间较原本递延。

芯片设计问题将不会只是英伟达所独有。供应链透露,这类问题只会越来越多,不过为了消除缺陷或为提高良率而变更芯片设计于业内相当常见。AMD CEO苏姿丰曾透露,随着芯片尺寸不断扩大,制造复杂度将不可避免地增加。次世代芯片需要在效能和功耗方面取得突破,才能满足AI数据中心对算力的巨大需求。

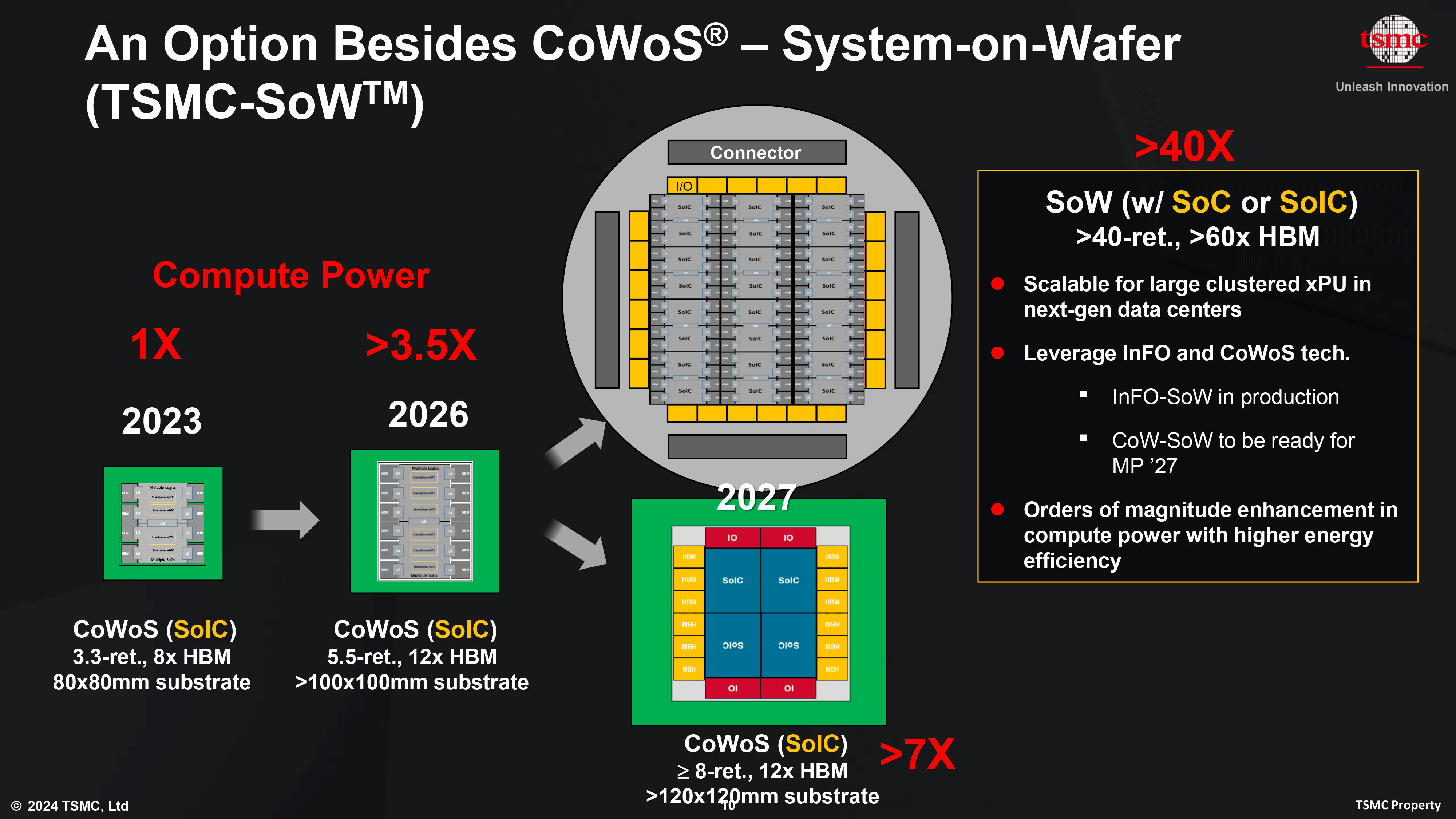

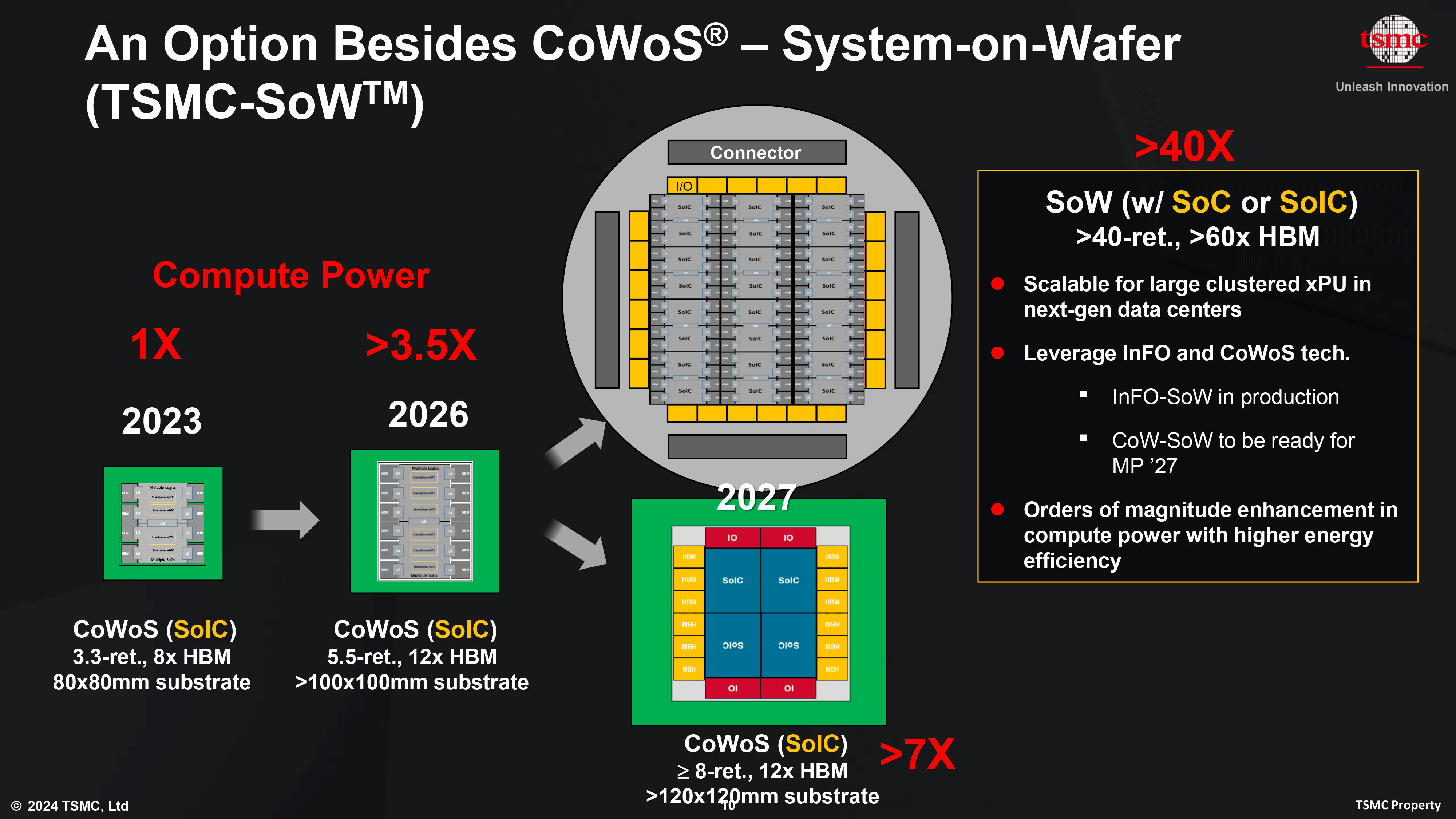

以开发全球最大AI芯片的Cerebras指出,多芯片组合技术难度将呈现指数级成长,强调“一整片晶圆就是一个处理器”,Cerebras的Wafer-Scale Engine(WSE)系列即采用AI领域知名的“晶圆级处理器”。依照台积电一直在发展晶圆级系统整合技术 InFO-SoW(System-on-Wafer),Dojo超级计算机训练区块(Training Tile)就是基于台积电InFO-SoW并已量产的首款解决方案。

因应大芯片趋势、及AI负载需要更多HBM,台积电计划结合InFO-SoW和SoIC为CoW-SoW,将内存或逻辑芯片堆栈于晶圆上,并预计在2027年量产。可预见的未来,将看到更多在整片晶圆上迭迭乐的巨无霸AI芯片出现。

![[图说]【喷嚏图卦20240808】让以色列痛苦的等待,也是惩罚的一部分-滴滴资源网](https://ddkd.net/wp-content/uploads/replace/39cb670e60a6c2a62de10a89fdaa6e31.jpeg)

![[图说]【喷嚏图卦20240802】人之为人的待遇-滴滴资源网](https://ddkd.net/wp-content/uploads/replace/c401f3d6aa5cb73bbf30bfffbdeb3ca8.jpeg)

暂无评论内容